核心架构

拾取四个x86指令、操作缓存指令、四个整数单元、两个存储/载入单元(支持72个乱序载入)、两个浮点单元(128-bit FMAC)、4-way 64KB一级指令缓存、8-way 32KB一级数据缓存、8-way 512KB二级缓存、8MB共享三级缓存

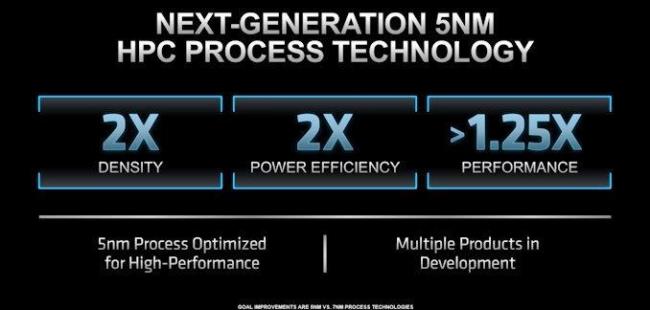

“Zen”核心采用了最新缓存层次结构,并改进了分支预测和同步多线程技术。这些先进设计将使“Zen”处理器核心极具弹性,以满足广泛的应用需求,其中包括无风扇2合1产品、嵌入式系统、高性能计算和数据中心。

原创 | 2022-09-29 10:00:09 |浏览:1.6万

核心架构

拾取四个x86指令、操作缓存指令、四个整数单元、两个存储/载入单元(支持72个乱序载入)、两个浮点单元(128-bit FMAC)、4-way 64KB一级指令缓存、8-way 32KB一级数据缓存、8-way 512KB二级缓存、8MB共享三级缓存

“Zen”核心采用了最新缓存层次结构,并改进了分支预测和同步多线程技术。这些先进设计将使“Zen”处理器核心极具弹性,以满足广泛的应用需求,其中包括无风扇2合1产品、嵌入式系统、高性能计算和数据中心。